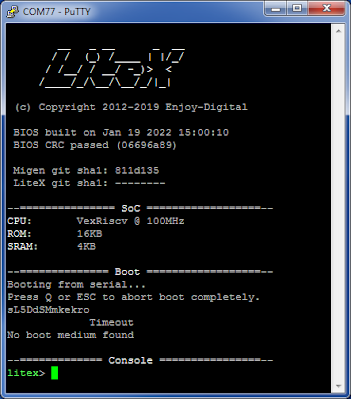

This is a quick and dirty guide about the process of how I got Litex to work on CR00103 board.

I have to admit that I have not generated any LiteX SoC designs lately. But I had some known working projects, so to start I did take the top.v and mem init files from one of the old known working projects.

Creating a new Radiant project and selecting the device. Adding files. I am copying the VexRiscv_min file also in a local folder so it is easily found in the project.

Creating PIN constraints. Done.

Well not yet there, the top.v I am using requires 100MHz clock, and I only have 12MHz on CR00103. So starting IP Wizard and generating PLL named mypll.

Changing the top verilog to use newly created wire clk100 and adding at the end:

mypll __(.clki_i(clk ),

.clkop_o(clk100 ));

No comments:

Post a Comment